# 29 A Short Introduction to Non-Ideal Op-Amp Behaviour

v1.5 – June 2021

Prerequisite knowledge required: Op-Amps, Linear Op-Amp Circuits, Non-Linear Op-Amp Circuits

#### 29.1 Introduction

As noted in the chapter introducing op-amps, the ideal op-amp has several characteristic features, including:

- 1. The input impedance is infinite (so no current ever flows into the inverting or non-inverting inputs)

- 2. The output impedance is zero (so it doesn't matter what load is connected to the output of the op-amp, the voltage on the output will remain the same)

- 3. The open-loop gain is effectively infinite (so when the output is within its linear range, the inverting and non-inverting inputs will be at the same voltage)

- 4. The op-amp has perfect differential gain (so the output will be zero when both inputs are at the same voltage)

- 5. The op-amp does not add any noise into the signal

- 6. The op-amp has infinite power supply rejection ratio (so any fluctuations on the power supply voltages do not affect the output voltage)

- 7. The op-amp has an infinite bandwidth (so the open-loop gain is not a function of frequency and the output can change immediately to reflect a change in the input)

However real op-amps do not have any of these properties. To design successful op-amp circuits it's important to know how op-amps deviate from the ideal, what effects these non-ideal behaviours have on real circuits, and what can be done to ameliorate these effects.

## 29.2 Finite input impedance: bias and offset currents

The current that flows into the terminals of real op-amps can most conveniently be divided into two different currents and treated separately. One is a constant DC current necessary for the input circuitry to work (the *bias current*), and the other is an AC current which reflects a small amount of the input signal.

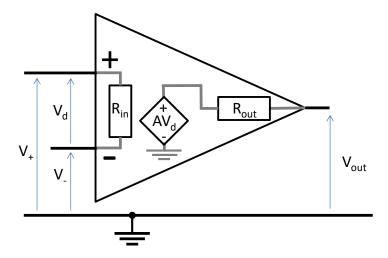

The latter current can be treated as due to a finite input resistance  $R_{in}$  and this can be modelled by a resistor between the two input terminals of the op-amp, as shown in Figure 29.1.

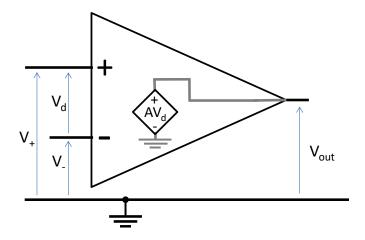

Figure 29.1 Op-amp model showing input and output resistance

This is not usually a problem: it is relatively easy to find op-amps that have input resistances of around  $10^{12}$  ohms, and the effect of negative feedback is to increase this still further (see the chapter on "Feedback" for more details).

However, there is also a DC current that flows into each input terminal, and this can have more serious effects on the circuits, especially when the circuit is required to operate with DC signals.

First two definitions: the input *bias current* is the small current that flows into each of the two inputs of the op-amp; the *offset current* is the difference between these two currents.

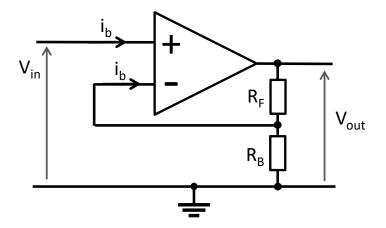

In many circumstances, the bias currents are not a problem provided they are equal (in other words, there is no *offset current*). This is because it is possible to compensate out their effects. For example, consider a non-inverting amplifier circuit:

Figure 29.2 A non-inverting amplifier showing the bias currents

If you include the bias currents in the analysis, the dc voltage gain of this circuit works out to be:

$$V_{out} = \frac{A\left(\frac{R_f + R_b}{R_f R_b}\right)}{\left(\frac{R_f + R_b}{R_f R_b} + \frac{A}{R_f}\right)} V_{in} + \frac{A}{\left(\frac{R_f + R_b}{R_f R_b} + \frac{A}{R_f}\right)} i_b$$

(29.1)

and in the usual case where the open-loop gain can be assumed to be very large, so that  $A / R_f >> (R_f + R_b)/(R_f R_b)$ , this can be accurately approximated as:

$$V_{out} = \left(1 + \frac{R_f}{R_b}\right) V_{in} + R_f i_b \tag{29.2}$$

So, the effect of a small input bias current is to produce a DC offset of  $R_f i_b$  in the output of the amplifier<sup>1</sup>.

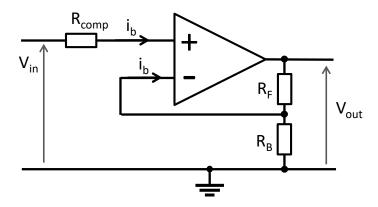

However, provided the bias currents into both inputs of the op-amp are the same, this DC offset can be compensated out quite easily: just put a resistor of value  $R_{comp}$  between  $V_{in}$  and the non-inverting input of the op-amp:

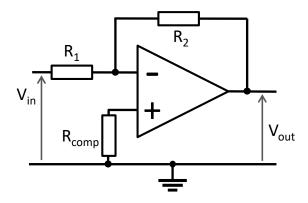

Figure 29.3 Non-inverting amplifier including the bias current compensation input resistor

Now the introduction of this resistor will mean that the voltage on the non-inverting input of the opamp is slightly lower than  $V_{in}$  by an amount  $i_b$   $R_{comp}$ . This in turn will change the output of the amplifier by an amount:

$$\Delta V_{out} = -\left(1 + \frac{R_f}{R_b}\right) i_b R_{comp} \tag{29.3}$$

If  $R_{comp}$  is chosen so that:

$$R_{comp} = \frac{R_f R_b}{R_f + R_b} \tag{29.4}$$

(in other words the parallel combination of  $R_f$  and  $R_b$ ) then the change in the output voltage will be:

$$\Delta V_{out} = -\left(1 + \frac{R_f}{R_b}\right) i_b \left(\frac{R_f R_b}{R_f + R_b}\right) = -i_b R_f$$

(29.5)

which exactly cancels out the effect of the bias current flowing into the inverting input.

<sup>&</sup>lt;sup>1</sup> This is one reason why it's not a good idea to use very large resistors in the feedback loop of a non-inverting amplifier: the larger the resistors, the larger the DC offset on the output due to the bias current.

One important point to note here: if the input  $V_{in}$  is not being driven from a voltage source, then the optimum value of  $R_{comp}$  calculated above includes the Thévenin output resistance of the source.

#### 29.2.1 A more intuitive way

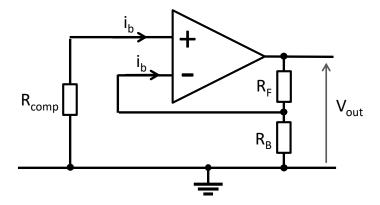

There is a more intuitive way to derive this result if you first assume that a solution does exist which provides no offset in the output. Consider what happens when the input  $V_{in}$  is set to zero (ground). The circuit looks like:

Figure 29.4 Non-inverting amplifier with bias current compensation and grounded input

Since the input is zero, we'd ideally like the output to be zero as well, and for an ideal op-amp that only happens when the voltages on the inverting and non-inverting inputs are equal.

The non-inverting input is connected to ground through a resistor of value  $R_{comp}$ . Assuming we've chosen  $R_{comp}$  correctly and therefore the op-amp output is at zero volts, the inverting input is effectively connected to ground through a parallel combination of  $R_f$  and  $R_b$ , both of which are at ground potential at one end.

The same current is being drawn into both inputs, so to get the same voltage on both input terminals of the op-amp, we need the compensation resistor  $R_{comp}$  to have the same value as the parallel combination of  $R_f$  and  $R_b$ .

#### 29.2.2 Inverting and summing amplifiers

A very similar analysis can be done for inverting amplifiers. Once again, the bias current, if included in the analysis, results in a DC offset in the output of the amplifier. However, once again, an additional resistor placed in the circuit can cancel out the effects.

In this case the compensation resistor is placed between the voltage reference (often ground) and the inverting input, as shown below:

Figure 29.5 Inverting amplifier with a bias current compensation resistor

A full analysis gives the same result as the more intuitive analysis, and while the intuitive method again requires the assumption that a solution does exist, it is considerably shorter and probably more instructive. So I'll just outline the intuitive method here, and leave the full analysis as an exercise for anyone interested.

Consider what happens when the input  $V_{in}$  to the circuit shown in Figure 29.5 is set to zero. Ideally, we would like the output to be zero as well, with no dc offset, and that requires the two inputs to the op-amp to be at the same voltage.

This time it is the inverting input which is connected to ground through  $R_{in}$  and  $R_f$  which are effectively in parallel (along with any other inputs if the circuit is summing amplifier), so the voltage on the inverting input will be:

$$V_{-} = i_{b} \left( \frac{1}{R_{f}} + \frac{1}{R_{in}} \right)$$

(29.6)

and the voltage on the non-inverting input will be:

$$V_{+} = \frac{i_b}{R_{comp}} \tag{29.7}$$

The only way these can be equal is if:

$$i_{b} \left( \frac{1}{R_{f}} + \frac{1}{R_{in}} \right) = \frac{i_{b}}{R_{comp}}$$

$$\frac{1}{R_{comp}} = \frac{1}{R_{f}} + \frac{1}{R_{in}}$$

(29.8)

and again, the value of the compensation resistor has to be the value of the input resistor(s)  $R_{in}$  and the feedback resistor  $R_f$  in parallel. Neat, isn't it?

### 29.2.3 The problem of offset current

What can't be so easily cancelled out is the offset current, since this can be either positive or negative (depending on the individual op-amp) and will usually vary with supply voltage and

temperature. Op-amp designers try and minimise the offset current, but it cannot be completely eliminated, and this does put a limit on the performance of DC op-amp amplifiers.

For example, consider the TL071: the datasheet specifies that the bias currents are typically 65 pA at 25  $^{\circ}$ C, but the offset current is typically 5 pA. Adding an additional resistor (see above) can eliminate the effects of the input bias current, but using a 100k resistor on the inputs suggests an additional voltage of 100k \* 5p = 0.5  $\mu$ V which is much more difficult to cancel out<sup>2</sup>.

(Reducing the value of the resistors in the circuit reduces the offset caused by the offset current, but this increases the power required in the circuit and may limit the gain that it's possible to achieve. As usual in circuit design, there is a trade-off to be made here.)

# 29.3 Non-zero output impedance

Look at the data sheet of an op-amp, and you might be surprised at the specification for the output impedance that you find: rather than being close to the ideal zero ohms, many op-amps have an open-loop output impedance of around 100 ohms.

However that doesn't mean that the actual output impedance of an amplifier built using the op-amp is 100 ohms. Negative feedback acts to reduce the output impedance of an op-amp, in this case by approximately the ratio of the open-loop gain to the amplifier's closed-loop gain<sup>3</sup>.

So, for example, an op-amp with an open-loop output impedance of 100 ohms and an open-loop voltage gain of around 200,000, when used in an amplifier stage with a gain of 10, has an effective output impedance of:

$$Z_{out} \approx Z_{out\_opamp} \times \frac{G_{DC}}{A_{DC}} = 100 \times \frac{10}{200,000} = 5 \text{ m}\Omega$$

(29.9)

At low frequencies, therefore, the output impedance of op-amps rarely causes any problems. However, it is worth noting that as the frequency increases (and therefore the open-loop gain of the op-amp decreases), the output impedance rises, and when approaching the unity-gain bandwidth<sup>4</sup> of the op-amp the output impedance can become significant.

### 29.4 Finite open-loop gain

There's no such thing as infinite gain, and while many op-amps have extremely large voltage gains at low frequencies (up to a million or so) this gain starts to drop with increasing frequency after a few tens of Hertz.

<sup>&</sup>lt;sup>2</sup> It could be attempted by trimming each individual circuit in production, but that is expensive, and in practice is not usually required.

<sup>&</sup>lt;sup>3</sup> See the chapter about "Feedback" for the details of why this happens and the derivation of equation (29.9).

<sup>&</sup>lt;sup>4</sup> Quick reminder: the unity-gain bandwidth of an op-amp is the frequency at which the open-loop voltage gain has a magnitude of one. (Note I have to write "has a magnitude of one" and not "is one" since there is a phase difference between the input and output. Using phasor notation, at the unity-gain frequency, the voltage gain of an op-amp is almost exactly -j.)

This means that at higher frequencies, approaching the bandwidth of the amplifier, all the results we obtained assuming that the open-loop gain was large are no longer valid. For example, at the 3-dB bandwidth of the amplifier:

- The difference in voltage between the inverting and non-inverting inputs is approximately the output voltage divided by the gain at DC (not zero)

- The output impedance is typically tens of ohms (which can be an issue if driving a low-impedance load such as a pair of headphones)

However at DC and frequencies a lot less than the 3-dB bandwidth of the amplifiers, you are unlikely to come across any negative effects due to the non-infinite gain of the op-amps.

# 29.5 Imperfect differential gain: offset voltages

Up until now, we've usually assumed that the ideal op-amp has a perfect differential gain. In other words it gives an output voltage given by:

$$V_{out} = A(V_{+} - V_{-})$$

(29.10)

where A is the open-loop gain of the op-amp. In fact, all op-amps have a small offset voltage  $V_{off}$ , which means that the output is actually given by:

$$V_{out} = A(V_{+} - V_{-} - V_{off})$$

(29.11)

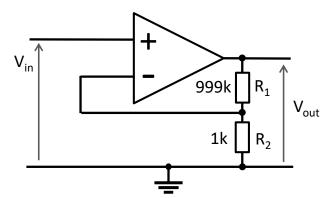

This can be an issue when attempting to get large gains from an op-amp. For example, consider an amplifier with a gain of 1000, such as might be required to amplify a very small output signal from a sensor:

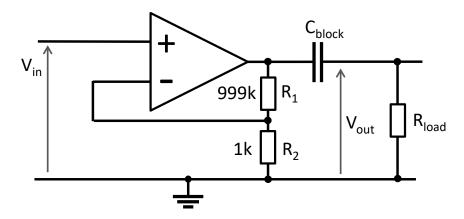

Figure 29.6 Non-inverting op-amp with a voltage gain of one thousand

Working through the derivation of the gain of this circuit gives an output of:

$$V_{out} = \left(V_{in} - V_{off}\right) \left(1 + \frac{R_1}{R_2}\right)$$

(29.12)

The ubiquitous TL071 op-amp has a maximum offset voltage of 10 mV, so that even with no input at all, this circuit could produce an output of up to +/-10 V. If it's powered from less than +/- 12V power supply, this could even saturate the op-amp.

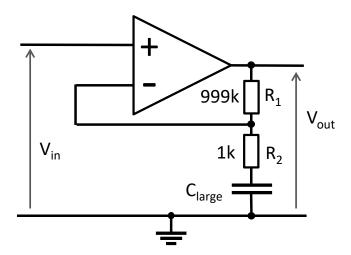

If you're not worried about the DC offset of the input signal (for example it's an audio signal, and frequencies below 10 Hz are not required), then there is a solution: use the circuit shown below in Figure 29.7.

Figure 29.7 Non-inverting op-amp with a voltage gain of one thousand at ac and voltage gain of one at dc

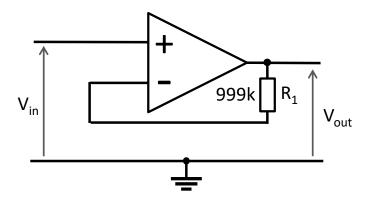

At higher frequencies (where the impedance of the large capacitor  $C_{\text{large}}$  is much less than the impedance of the resistor  $R_2$ ), this circuit behaves just like the circuit shown above in Figure 29.6. However at DC, where the impedance of the large capacitor is infinite, this circuit effectively becomes:

Figure 29.8 Non-inverting amplifier at dc with low-frequency gain-limiting capacitor open-circuits

which has a voltage gain of one, and therefore in this example a maximum output offset voltage of 10 mV.

Another approach to reduce the DC offset at the output of the amplifier is to add a DC blocking capacitor to the output of the op-amp, as shown in Figure 29.9. Provided the capacitor is large enough so that for all frequencies of interest the impedance of the capacitor is much smaller than the input impedance of the amplifier's load, this can remove all the amplified DC offset without affecting the signal.

Figure 29.9 Non-inverting amplifier at dc with dc blocking capacitor on the output

However this latter solution doesn't help with the problem that an op-amp with sufficiently large gain can be driven into saturation by the offset voltage.

#### 29.6 Noise and op-amps

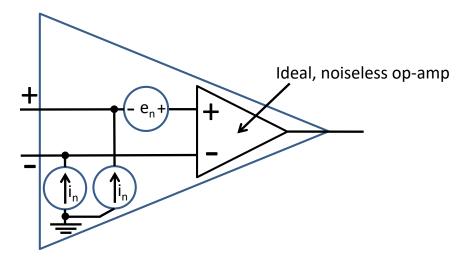

All active circuits introduce additional noise into the circuit. The additional noise added by an opamp is usually specified in two different parameters in the data sheets: noise voltage  $e_n$  and noise current  $i_n$ . This reflects the equivalent noise model of an op-amp, which looks like this:

Figure 29.10 A simplified op-amp noise model

This means that from a noise point of view, an op-amp behaves like an ideal noiseless op-amp, with a source of current noise going from ground into each input, as well as a noise voltage adding to one input. It's important to note that the two noise currents sources have the same average power, but they are completely uncorrelated.

To calculate the output noise, you would need to know the effective impedance attached to each input (the parallel combination of all the resistors attached to each input). This allows you to calculate the total noise voltage, which when multiplied by the gain of the circuit, gives the total output noise.

The effect of these equivalent noise in op-amps in op-amps is considered in much more detail in the chapter on "Noise".

# 29.7 Power supply rejection

Power supply rejection is the ability of an op-amp to continue to produce an output defined only by the voltages on its two inputs, irrespective of any variation in voltage on the power supply. It's measured in terms of the Power Supply Rejection Ratio (PSRR) which is the ratio of a change of the power supply voltage to the change in the output voltage of the op-amp.

Ideally, the PSRR should be infinity (since the output voltage should not change at all); in practice values of between 70 and 100 dB are typical. To put this into context, a PSRR of 90 dB would suggest that a one-volt peak-to-peak variation on the power supply input (for example a positive power supply that varied between 11.5 and 12.5 volts) would result in a variation in the output of 31.6  $\mu$ V peak-to-peak.

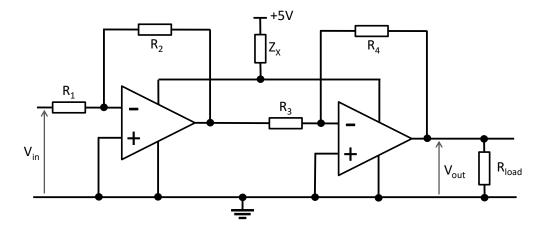

This might not sound like much, but it can be a real problem. For example, consider a two-stage amplifier with a large gain, sharing the same power supply, as shown in Figure 29.11. For simplicity, I have assumed that this is a single-rail op-amp powered from five volts.

The second (output) stage is driving a large AC current into the load resistor  $R_{load}$ . This means that it is taking a large, changing current from the power supply (there's nowhere else it can come from). No power supply is perfect, and I've drawn this one as an impedance  $Z_X$  in series with a perfect 5V voltage source; in practice this impedance could be mostly due to inductance and resistance in the wires in the circuit.

Since there is a constantly-changing current flowing from the power supply, there will be a corresponding change in the voltage generated across  $Z_X$ , and that will result in the output signal appearing as a fluctuation in the power supply to the first stage of the amplifier. Due to the finite PSRR, this results in a change in the signal appearing on the output of the first-stage of the amplifier.

Figure 29.11 Two-stage amplifier with shared power supply

If there is sufficient gain, and the PSRR is not sufficiently high, then this small signal at the output of the first stage can be amplified by the second stage sufficiently to produce enough output signal to produce a greater current, and therefore more fluctuations on the power supply, and thereby a larger output signal from the first stage, and so on. The result is an unstable oscillation.

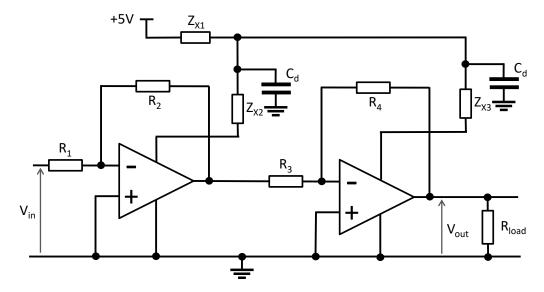

In these circumstances what is required is to separate out the power supplies for the two stages of the amplifier as much as possible, for example like this:

Figure 29.12 Two-stage op-amp amplifier with isolated power supplies

Here additional decoupling capacitors have been added to each amplifier, so that any variation in the current required by the output stage can be supplied from the charge in the capacitor, and does not need to come from the +5V supply itself (which would cause a drop in the potential across  $Z_{X1}$  and hence cause some interference in the output of the first stage amplifier).

However this is impossible to do when both stages of the amplifier are built using two op-amps in the same package, sharing the power pins. This is why when building a two-stage high-gain op-amp amplifier, it's a very good idea to have the two amplifier stages in different integrated circuits. If you tried to build the same circuit using two op-amps in the same package, it could easily oscillate (or at least exhibit some resonant-like gain at higher frequencies).

## 29.8 Finite bandwidth and the gain-bandwidth product

No real op-amp has an infinite bandwidth. This results in the open-loop gain decreasing as the frequency increases, and in many cases the open-loop gain can start to fall at what may be a surprisingly low frequency (well below 100 Hz). However this doesn't mean that the closed-loop gain of the amplifier will necessarily start dropping at such low frequencies as well: the 3-dB bandwidth of these amplifiers is usually much higher.

This is such an important effect that there is an entire chapter devoted to it: please see the chapter about "Op-amp Bandwidths" for more details.

#### 29.9 Slew rates

An ideal op-amp could be drawn something like this:

Figure 29.13 Ideal op-amp model

where the output voltage  $V_{out}$  is given by the gain A times the difference between the input voltages  $V_d$ . However, if you look inside an op-amp, this simple approximation misses out an intermediate stage. What's actually going on inside a typical op-amp is something more like this:

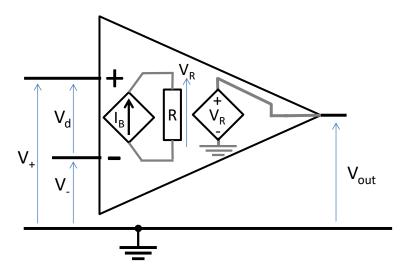

Figure 29.14 Op-amp showing internal current source

There is a current source which has a value dependent on the difference between the input voltages, for example it could be written:

$$I_{B} = kV_{d} = k(V_{+} - V_{-})$$

(29.13)

and that produces a current across a resistor R. It is the voltage across this resistor  $V_R$  which then determines the magnitude of the output voltage  $V_{\text{out}}$ .

The current source can either sink or source current into the resistor to produce positive or negative output voltages, but it has a maximum value: the current cannot exceed a certain value. This circuit, in combination with the method the op-amp uses to limit the bandwidth of the circuit, produces a limit on how fast the output of the op-amp can change.

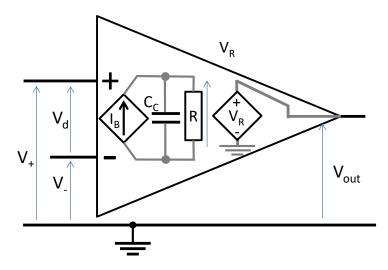

The limit results from the fact that most op-amps limit their bandwidth using an internal capacitor, which can be thought of as being in parallel with the internal resistor R:

Figure 29.15 Equivalent op-amp circuit showing the internal bandwidth limiting capacitor

If the input voltage suddenly changes, the current source will suddenly change as well, but the voltage across the internal resistor won't immediately reflect the change in the input: the capacitor has to charge/discharge. Since the capacitor is being charged or discharged from a current source, this will be a linear charging rather than an exponential charge: a constant amount of charge (the maximum the current source can provide) will be arriving at/leaving the capacitor per second.

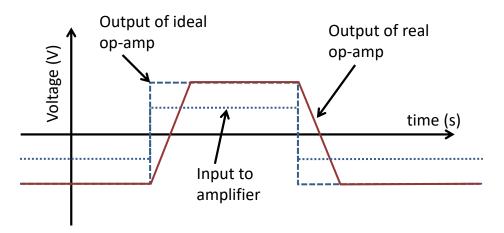

This means that when the input undergoes a step-change, the output will ramp up to the final value as the capacitor charges, giving an output which looks something like this:

Figure 29.16 Input and output of real op-amp amplifier with a gain of two

The gradient of the ramp is known as the *slew rate* of the amplifier<sup>5</sup>, and is usually specified in units of  $\mu V/s$ . If you want an op-amp to be able to handle large signals at high-frequencies without introducing this sort of distortion, a high slew rate is required.

This is not only a problem for square-wave inputs: any signal which requires the output voltage to change at a rate greater than the op-amp's slew-rate will suffer some distortion. For example, a

$<sup>^{5}</sup>$  The slew rate of the TL071 is specified as 13 V/ $\mu$ s. This means that the minimum time it would take a TL071 to change its output by one volt would be 1/13  $\mu$ s = 77 ns.

sine-wave of frequency *f* Hz and peak-to-peak amplitude *A* will require a maximum rate of change in the output voltage of:

$$\max\left(\frac{dV}{dt}\right) = \max\left(\frac{d\left(\frac{A}{2}\sin(2\pi ft)\right)}{dt}\right) = \max\left(\frac{A}{2}2\pi f\cos(2\pi ft)\right) = A\pi f \qquad (29.14)$$

If this exceeds the amplifier's slew rate, then distortion will result.

Put this another way: the op-amp can provide an undistorted output for an input sine wave provided the peak-to-peak amplitude satisfies:

$$A < \frac{\text{slew rate}}{\pi \times f} \tag{29.15}$$

Sometimes op-amps provide graphs of maximum peak-to-peak output swing against frequency; it is the slew rate that limits the maximum amplitude A at high frequencies.

# 29.10 Summary: the most important things to know

- Op-amps have input offset voltages, and provide an output given by  $V_{out} = A(V_+ V_- V_{off})$

- Op-amps require a small input current (known as the bias current). This produces a DC

offset on the output, although provided the bias currents into the inputs are equal, this

offset can be eliminated with a compensating resistor.

- The offset current is the difference between the bias currents and is much harder to compensate for.

- There is a maximum rate at which the output of an op-amp can change voltage, this is known as the slew-rate.

- Op-amps have a finite output impedance, but the use of negative feedback can reduce this to negligible levels at low frequencies.

- Ideally the output voltage of an op-amp would not change when its power supplies change in voltage, but in practice it does; this is quantified by the power supply rejection ratio.

- For more details about the finite bandwidth of op-amps, see the chapter on "Op-amp amplifier bandwidths", for more details about the noise performance of op-amps, see the chapter on "Noise".